# Open-Source Robotics and Process Control Cookbook

Designing and Building Robust, Dependable Real-Time Systems

Lewin A. R. W. Edwards

# Open-Source Robotics and Process Control Cookbook

# Open-Source Robotics and Process Control Cookbook

Designing and Building Robust, Dependable Real-Time Systems

by Lewin A.R.W. Edwards

Newnes is an imprint of Elsevier 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA Linacre House, Jordan Hill, Oxford OX2 8DP, UK

Copyright © 2005, Elsevier Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, e-mail: permissions@elsevier.com.uk. You may also complete your request on-line via the Elsevier homepage (http://elsevier.com), by selecting "Customer Support" and then "Obtaining Permissions."

Recognizing the importance of preserving what has been written, Elsevier prints its books on acid-free paper whenever possible.

#### Library of Congress Cataloging-in-Publication Data

(Application submitted.)

#### British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library.

ISBN: 0-7506-7778-3

For information on all Newnes publications, visit our Web site at www.books.elsevier.com

04 05 06 07 08 09 10 9 8 7 6 5 4 3 2 1

Printed in the United States of America.

### **Dedication**

This book is dedicated to my wife Cristen, in recognition of her uncomplaining acceptance of yards of PVC conduit in hallways, pounds of gel-cells in the living room, and never-ending snarls of wire and motors throughout the house.

## **Contents**

| About the Author                                                                            | xi  |

|---------------------------------------------------------------------------------------------|-----|

| What's on the CD-ROM?                                                                       | xii |

| Chapter 1: Introduction                                                                     | 1   |

| 1.1 History of this Book and What You'll Get From Reading It                                | 1   |

| 1.2 Target Readership and Required Skills and Tools                                         | 5   |

| 1.3 Conventions Used in the Text                                                            | 7   |

| Chapter 2: Microcontrollers, Single-Board Computers and Development Tools                   | 9   |

| 2.1 The Division of Labor                                                                   |     |

| 2.2 Candidate Microcontrollers for 'Hard' Tasks                                             | 13  |

| 2.3 The Atmel AVR and its Development Hardware Up Close                                     | 17  |

| 2.4 Candidate x86-based SBCs for 'Soft' Tasks                                               | 21  |

| 2.5 The Advantech PCM-5820 Single-Board Computer Up Close                                   | 27  |

| 2.6 Selecting an Inter-Module Communications Protocol                                       | 32  |

| Chapter 3: Some Example Sensor, Actuator and Control Applications and Circuits (Hard Tasks) | 41  |

| 3.1 Introduction                                                                            | 41  |

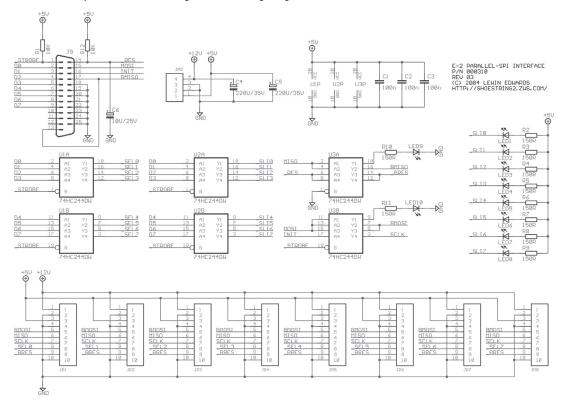

| 3.2 E2BUS PC-Host Interface                                                                 | 44  |

| 3.3 Host-to-Module Communications Protocol                                                  | 49  |

| 3.5 Speed-Controlled DC Motor with Tach Feedback and Thermal Cutoff70 3.6 Two-Axis Attitude Sensor using MEMS Accelerometer                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.7 RS-422—Compatible Indicator Panel                                                                                                                                                               |

| Chapter 4: The Linux-Based Controller (A Soft Task)                                                                                                                                                 |

| 4.1 A Brief Introduction to Embedding Linux on PC Hardware                                                                                                                                          |

| 4.2 Configuring the Development System and Creating Our Custom Kernel117 4.3 The Linux Boot Process—Creating a Bootable CompactFlash Card123 4.4 Creating a Root Filesystem for our Embedded System |

| 4.3 The Linux Boot Process—Creating a Bootable CompactFlash Card123 4.4 Creating a Root Filesystem for our Embedded System                                                                          |

| 4.4 Creating a Root Filesystem for our Embedded System                                                                                                                                              |

| 4.5 Creating a Bootable Linux System-Restore CD-ROM Disc                                                                                                                                            |

| 4.6 Using the Parallel Port as a General-Purpose I/O Interface in Linux142 4.7 Implementing Graphical Control Interfaces                                                                            |

| 4.7 Implementing Graphical Control Interfaces                                                                                                                                                       |

| 4.8 Infra-Red Remote Control in Linux Using LIRC                                                                                                                                                    |

| 4.9 Introduction to Machine Vision Using Video4Linux                                                                                                                                                |

| 4.10 Customizing Your BIOS—The Structure of a Modern BIOS201  Chapter 5: Encryption and Data Security Primer                                                                                        |

| Chapter 5: Encryption and Data Security Primer209                                                                                                                                                   |

| ,                                                                                                                                                                                                   |

| 5.1 Introduction 200                                                                                                                                                                                |

| 3.1 Introduction                                                                                                                                                                                    |

| 5.2 Classes of Algorithm                                                                                                                                                                            |

| 5.3 Protecting One-Way Control Data Streams217                                                                                                                                                      |

| 5.4 Protecting One-Way Telemetry                                                                                                                                                                    |

| 5.5 Protecting Bidirectional Control/Data Streams220                                                                                                                                                |

| 5.6 Protecting Logged Data222                                                                                                                                                                       |

| 5.7 Where to Obtain Encryption Algorithms224                                                                                                                                                        |

| Chapter 6: Expecting the Unexpected                                   | 227 |

|-----------------------------------------------------------------------|-----|

| 6.1 Introduction                                                      | 227 |

| 6.2 Dangerous Exception Conditions and Recovering From Them           | 228 |

| 6.3 On-Chip vs. Off-Chip Watchdog Hardware                            | 230 |

| 6.4 Good Power-On Reset Practices                                     | 232 |

| 6.5 A Few Additional Considerations for Battery-Powered Applications. | 235 |

| Chapter 7: Contents of the Enclosed CD-ROM                            | 237 |

| Index                                                                 | 237 |

### About the Author

Lewin A.R.W. Edwards was born in Adelaide, Australia. He worked for five years in Melbourne, Australia on government-approved encryption, desktop protection and data security products for DOS, Windows and OS/2. For the next five years, he worked in Port Chester, New York for Digi-Frame, Inc., where he designed both the hardware and firmware of a range of multimedia digital picture frame appliances. These devices ranged in complexity from small pocket-size still-image viewers up to fully networked wall-mounted devices with audio and full-motion video support. He currently lives in New York City and works as a short-range radio digital design engineer for a well-known manufacturer of wireless security and fire safety products. His earlier works include *Embedded Systems Design on a Shoestring*, (a book about low-cost embedded systems development, principally targeted at ARM7 platforms), as well as articles on specialized design considerations for the microcontrollers used in electronic toys, commentary on Universal Plug'N'Play, reverse-engineering Internet appliances, and other topics of interest.

### What's on the CD-ROM?

### Included on the accompanying CD-ROM:

- A free version of the schematic capture and PCB CAD software used to prepare this book. (Refer to the license agreement included with the software for usage restrictions and limitations.)

- Atmel AVR Studio® 4.08.

- Full schematics and sourcecode for the projects described in this book.

- Ready-made disk images for the miniature Linux distribution used as a basis for the book's PC-side software.

- Distribution archives of the sourcecode for all GNU software used, along with application-specific patches, where appropriate.

# CHAPTER

### Introduction

### 1.1 History of this Book and What You'll Get From Reading It

Over the course of roughly a year, after completing my first book, I resurrected an old pet project of building an autonomous submarine (referred to as the E-2 project) with certain fairly challenging functionality requirements. In the course of developing this idea, I spent many hours on the Internet and elsewhere, researching techniques for rapid development of various electromechanical control systems and platforms to run fairly complex signal-processing algorithms. Although there are, of course, thousands of useful projects and snippets of information to be obtained from the Internet and books on hobbyist robotics, I found that nobody else seemed to have my exact priorities. In particular, there is apparently no single reference that gathers together at least introductory solutions to all the embedded design issues that affected my project: a need to use low-cost (open-source) tools and operating systems, a requirement for several features with fairly hard real-time requirements, and a desire to use cheap, off-the-shelf consumer grade components wherever possible. Available resources on many topics concentrate either on very expensive off-the-shelf industrial components, or on tightly constrained systems built around a single microcontroller, with delicately optimized, nonportable code to control peripherals—and a very limited range of peripheral support, at that. These latter system design restrictions are unavoidable when you're working to tight power requirements, space constraints, or a rock-bottom bill of material (BOM) cost, but it's an inordinate amount of effort to build and tune such systems for a one-off project or a prototype. Furthermore, learning all the details required to assemble such a system is an enormous task; it's easy to get lost in fine-tuning details without ever managing to field a complete, working system. Irritatingly, many of the tweaks and most of the careful planning you do to get that system operational will have to be thrown away if you move into actual production, or if you need to build some more units with slightly different components.

What I was searching for while developing the E-2 project was a way to build various hard real-time modules (sensors and actuators) that could easily and cheaply be interfaced to a general-purpose computer running Linux. The Linux box served as a testbed for algorithms which would later be ported down into a smaller, cooler, more power-efficient processing module of some kind. I needed a solid basis of known-good code and techniques so that I could strike out from that point and build my own customized system. I also wanted a simple up-and-running guide to building embedded Linux distributions. For the initial, nonfieldable prototype of my submarine, I didn't have an exact idea of how much CPU horsepower I would need in the final version—so I didn't want to get tied to a specific microcontroller architecture, nor did I want to get bogged down in trying to tweak and tune many real-time tasks on a single microcontroller. I also wanted to use a few peripherals—such as cameras —which are easiest interfaced through a general-purpose operating system.

These requirements may sound a chord with your own working life. Chances are you've encountered situations where it would be useful to automate some long-term data-gathering experiment or create a simple automated controller for a programming, manufacturing or other task. In this vein, three other instances where I have applied the techniques in this book are:

- The development of a range of successful (commercially-fielded) networked multimedia appliances, designed for unattended advertising and art-gallery applications.

- The development of specialized, almost wholly automatic mechanical failure testing apparatus for certain consumer electronics articles.

- Construction of an automatic high-speed datalogger that monitors a radio link and extracts DTMF messages targeted at specific receivers.

The second item above is of particular interest, because it demonstrates nicely how this book can be of practical value in process control and testing applications. During 2002, I briefly worked for a small division of a multinational company whose

major focus was household and office plasticware. It was most instructive to examine their automated test fixtures—proprietary systems—and compare the cost and setup complexity of these fixtures with the relatively low cost and setup time of a simple Linux-based SBC controlling the same pneumatic actuators and sensors. Clearly, there is an under-exploited market for low-cost test systems of this type. The proprietary systems in use at this particular facility cost almost \$20,000 for a half-dozen actuators and the associated PLCs, plus uncounted hours of setup time<sup>1</sup>. The control software for these devices was specialized and not well-understood; in fact, most of this equipment was standing idle because the people who originally configured it had left the company. By way of contrast, the same tasks could easily be accomplished with a regular PC costing a mere few hundred dollars, plus perhaps \$200 per actuator for the associated pneumatics. More importantly, the control software for such a system is a simple C program easily understood and adaptable by any competent computer science or electronic engineering major; there were several candidates readily available in the company lab.

Due to the nature of the research which led to this book's inception, I have included a sprinkling of naval details within the text, not all of which are directly relevant to the embedded engineer. If this material is not of interest, you can safely ignore it without compromising your understanding of the remaining text in any way. The reason this information is included alongside the "pure" embedded development discussion is principally to illustrate the real-world requirements and thinking that led to various design decisions in the E-2 project. Engineering is not theoretical science; it is an applied discipline, and it is with this in mind that I use specific examples to illustrate theoretical points.

You should also note that some of the opinions expressed in this book, if not exactly controversial (except by Usenet standards—*everything* on Usenet is controversial!), are at least arguable; for example, the choice of AVR as my real-time control platform. For this reason, I have provided additional justification for the decisions I have made in this text. This additional explanation should demonstrate the reasons I had for choosing specific paths, but it's expressly *not* designed to prosely-

<sup>&</sup>lt;sup>1</sup> The system was originally set up by "free" interns, so their time wasn't rigorously tracked.

tize the AVR to people who have experience with, and prefer, another architecture. Again, this "bonus material" is not critical to your understanding of the basic concepts presented here, and you can safely skip it if you wish.

Also keep in mind that this book is intentionally not a "bible." It is not an exhaustive coverage of every single nuance of the topics covered; such a work would span several shelves. The primary goal of this book is to describe and illustrate a simple, modular, inexpensive methodology for implementing complex embedded systems, and to present some ready-to-use modules for the reader to adapt to his or her own projects. The particular emphasis is on realizing end-to-end solutions using low-cost development hardware and free software tools. By the time you reach the last few pages, hopefully you should have the following:

- A functional understanding of the critical "under-the-hood" details required to bootstrap Linux on x86 platforms.

- An introduction to the types of problems you will face in using embedded x86 single-board computers as the core of data logging and motion-controlling systems.

- Basic information about the Atmel AVR microcontroller family.

- A practical introduction to building some simple data acquisition and motor control circuits, and connecting them to PCs.

- Some basic "primer" information on data security, authentication and reliability issues as they affect embedded systems.

The underlying idea is that the reader has reasonably intimate experience with one or other of the topics of Linux application development, or development of deeply embedded systems—this book is designed to boost you up the leading edge of your learning curve with the essentials of whichever side of the equation you're missing. It also provides the glue that binds these pieces of information together in the overall context of a fairly complex project. Note, by the way, that I used the titular word "cookbook" with some diffidence. Purely cookbook engineering—slotting ill-understood pieces together like Capsela spheres—is never good practice. In this book, I'm giving you some ready-to-use Capsela pieces, but I'm also telling you how

and why I made the gears and shafts in each piece, and to some extent how you can go further and make better pieces for yourself. These explanations are much more important than the blueprints for the pieces themselves.

When planning a book like this, it's easy to fall into one of two traps: either to create a single, monolithic "mega-application" which illustrates all the desired points, but is extremely difficult to explain succinctly, or on the other hand to break the topic down into numerous small abstract notes that many readers will have trouble integrating into real-world projects. I have tried to steer between these two extremes by breaking the more interesting modules of the E-2 project into a few small, practical applications together with basically standalone code and enough theory to modify and extend these applications for your own uses.

Finally, a note to people who own my previous book, *Embedded System Development on a Shoestring*. This book is not designed to be a sequel to that volume, but it is definitely related material. If you follow the techniques in this book to build a prototype device, and you later want to squeeze it down into an optimized single-chip solution, my earlier work will help you understand how to use free GNU tools to get your software easily ported across to an ARM microcontroller. The principal criticisms I received for that previous book were that it needed to cover a wider range of information, and that there were too few illustrations, making it a rather dry read. I've listened to these comments and I hope you will find this book satisfies your needs in both respects. As always, your comments and suggestions are welcome; you can email me at sysadm@zws.com or visit my web site at <a href="http://www.zws.com/">http://www.zws.com/</a>.

### 1.2 Target Readership and Required Skills and Tools

Throughout this text, I assume that the reader is a competent C programmer, with some experience in using (though not necessarily embedding) UNIX-like systems, specifically Linux. I also assume a very basic level of knowledge of real-time systems and simple digital electronics. This book is not an introduction to Linux, nor is it an introduction to the concepts of embedded programming; there are hundreds of such books already.

In order to follow along with the examples in this book, you will need the following:

- An x86-based PC system running Linux. This book was developed using Fedora Core 1, which can be downloaded for free (or purchased on CD) from <a href="http://fedora.redhat.com/">http://fedora.redhat.com/</a>. A full Linux distribution is not included with this book due to disk space constraints. For simplicity's sake, I suggest you use Fedora Core 1 unless you have special reasons for using a different distribution.

- Ideally, an x86-based SBC selected from the list in Section 2.5, with a hard drive and CD-ROM drive attached, and a CompactFlash® card of at least 8 MB capacity—however, none of these items are absolutely essential.

- A means for burning AVR microcontrollers. There are numerous schematics for simple AVR programmers available freely on the Internet, and a minimal programmer is simple to breadboard. (More on this in Section 2.3). I specifically recommend the STK500 development board from Atmel, because it is fully integrated with Atmel's AVR Studio IDE, and the \$79 price is better value than the effort of building a comparable development system from schematics.

- An AVR development environment, or at least an assembler. The projects in this book were developed using the free Windows®-based AVR Studio® from Atmel, which is included on the CD-ROM. Pure-Linux shops may prefer to use the free avrasm assembler, which I have also included. The avrdude package can be used to burn chips under Linux.

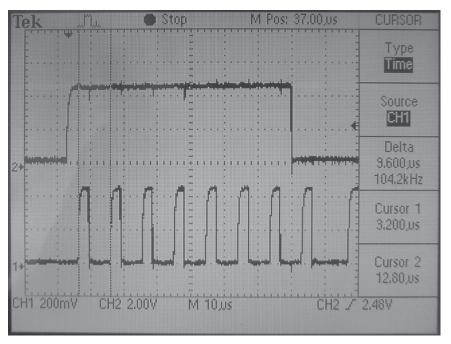

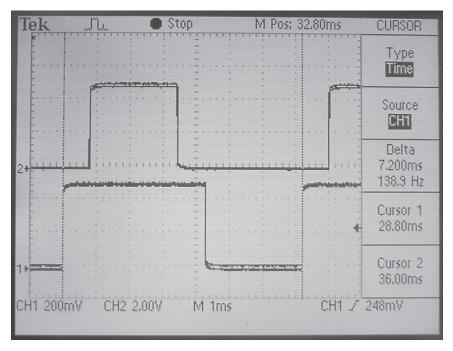

- An oscilloscope is highly recommended, though not mandatory. When you're debugging serial communications protocols in particular, nothing beats being able to see the actual bits going to and fro. The waveform screenshots in this book were taken using a Tektronix TDS210 60 MHz two-channel digital scope.

### 1.3 Conventions Used in the Text

Throughout this book, I have attempted to adhere to a single set of conventions:

- For the sake of consistency, all measurements are given in metric units, *except* where they refer to a controlling dimension that was originally specified in nonmetric units. In the latter case, the controlling dimension is specified in its native unit, and the metric equivalent is shown in parentheses, as in "The length of a foot-rule is 12 inches (30 cm)." In some cases, this results in a departure from accepted industry standards; for example, the speed of a seagoing vessel is normally specified in knots (nautical miles per hour), not ms<sup>-1</sup>.

- URLs are written in italics, for example, *http://www.zws.com/* in order to separate them from surrounding punctuation.

- In common with most other technical publications, sourcecode and command line text that is intended to be typed verbatim is rendered in a fixed-space font.

- Occasionally, you will find UNIX commands and library functions mentioned with the standard nomenclature of command(n), where n is the section containing the manual page for the command in question. For example, you can find out more about rdev(8) by typing man 8 rdev at a shell prompt. Don't go looking for nonexistent footnotes!

- When I discuss procedures that access the enclosed CD-ROM from Linux, I assume that the disk is mounted at /mnt/cdrom, because that is where most desktop Linux distributions will put it. If you mount it somewhere else, you'll need to edit your command-line entry appropriately.

- All sourcecode and makefiles are designed to be viewed with a tab width of four character spaces.

# Microcontrollers, Single-Board Computers and Development Tools

#### 2.1 The Division of Labor

The designer of a complex multi-level project such as the E-2 must frequently juggle the following conflicting requirements, among others:

- Hard real-time response requirements of sections of the overall system.

- The hardware and firmware complexity of interfacing special peripherals such as cameras, Ethernet networking, 802.11b wireless networking, and others.

- Bill-of-materials costs for both prototypes and production pieces.

- Development time.

- Cost of development tools.

- Relatively high cost of components designed for embedded systems, as compared to the pricing of comparable-performance, generally-available consumer products.

It's a terribly daunting task to approach all of these problems at once, particularly at the start of a project when your exact needs are generally not well-specified. Limited time or monetary budgets add stress, because there simply may be no days or dollars spare to be wasted exploring dead-end research paths on the way to a working system. Furthermore, many of the systems of interest to readers of this book will either be unique, or will be produced in very small volumes. For such systems, it's hard to justify intense time expenditures researching and fine-tuning noncore features (i.e., the infrastructure features you have to debug before you can debug the functionality you actually want to develop).

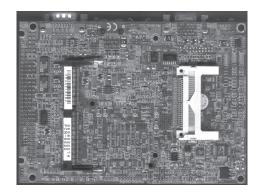

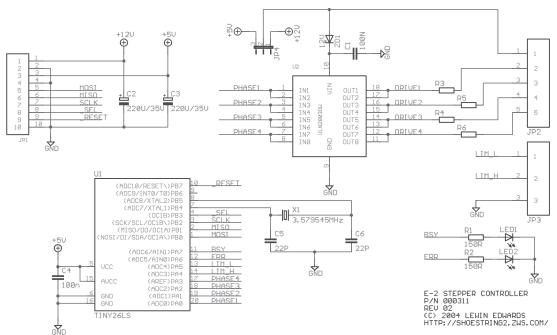

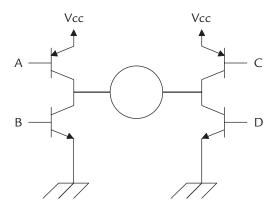

The basic methodology I have used to cut through most of this Gordian knot is as follows: To begin with, I divide all the system processes into two categories, which I will term "hard" and "soft." For the purpose of this discussion, hard processes are defined as direct physical-world interaction tasks where timing and system robustness are likely to be critical to performance and/or safety. Examples in the E-2 system are: Stepper motor control for rudder and dive planes, battery charge and thermal monitoring, depth monitoring, propulsion motor control, and bilge sensors. Hard processes are typically easy to identify and characterize precisely, and can often be implemented in a small 8-bit microcontroller. In the E-2, we will perform all the hard tasks using microcontrollers in the AVR series, from Atmel.

By contrast with hard processes, soft processes are not at all mission-critical, and have relaxed or nonexistent real-time requirements. Generally, soft tasks can crash, provide erroneous, untimely or downright missing data, and the overall system health will not be unduly compromised. Examples in the E-2 project are image capture, storage and analysis, data logging, and some telemetry functions. Many soft tasks require interaction with complex sensory or communications modules such as cameras and wireless networks. For this reason, it is convenient to use standard off-the-shelf consumer peripherals such as USB webcams, CompactFlash storage media, USB wireless LAN pods, and others. Interfacing to these sorts of peripherals from a small microcontroller is often decidedly nontrivial—oftentimes, technical data is hard to come by, and it's also frequently difficult to acquire loose sample parts in small quantities. Prototyping with these parts is also usually difficult.

In the case of low-cost CMOS image sensors, for example, virtually the only way to get these parts off the shelf is to buy a complete camera and cannibalize it—IF you can identify the devices in it without microscopic examination, and IF you can get datasheets! Furthermore, manufacturers of consumer electronics are more or less constantly refining and costing down their products. You may cannibalize MyWidget V1.0 and spend many hours getting the components to work in your system, only to find (when you start to build a second unit, e.g., to replace a lost prototype) that MyWidget V1.0 has been superseded by V1.1, containing totally different components—maybe even an undocumented ASIC.

In a similar manner to the way I handled task management, I divide system communications into two classes; control-critical and noncritical. In the case of E-2, all control-critical data transfers occur within the vehicle itself, between the various real-time modules and the main controller. These communications take place over an internal three-wire SPI-style serial bus. Noncritical communications are, for example, the ship-to-shore telemetry link. These data streams can be carried using whatever media and protocols are convenient, with less attention paid to real-time issues such as lag<sup>2</sup>.

You may wish to pause here and consider the implications of the preceding decisions. In particular, note the implication that hard tasks and control-critical links are trusted and soft tasks and noncritical links are not trusted. We're going to be running all the hard, critical stuff in small microcontrollers carefully programmed "to the metal," and—hopefully—completely understood and characterized in all conceivable situations. The messy stuff like networking, snapping pictures to a hard drive, and so on, will all be run on a totally separate piece of hardware. If it crashes, it can simply be reset or shut down with no impact on system survivability. This is important, because most of the software running on that untrusted piece of hardware wasn't developed for embedded use, and it certainly isn't as well-defined as the software we custom-engineered into the hard-task controllers.

I should stress that none of the previous discussion is *per se* an indictment of the reliability of embedded Linux. It is perfectly possible to build rock-solid control systems based around a single Linux processor, and there are many such systems in existence. However, a uniprocessor system requires considerable fine-tuning of the operating system and application software to achieve a sufficiently real-time end result<sup>3</sup>. Furthermore, in order to achieve such a result, it is often necessary to use nonstandard software components intended specifically for embedded systems (real-

Obviously, this isn't true of all telemetry applications. In E-2, the telemetry signal is provided solely as a convenience to the shoreside operator; it's not critical that it be strictly real time or that it implement strenuous error correction.

<sup>&</sup>lt;sup>3</sup> Uncharitable people say of embedded Linux that the standard development technique is to write the device driver or application the way you think it should be written, then add hardware until it performs successfully, to the desired approximation of "real time." The fact that this is so often true is more an indictment of the developers than the OS, though.

time Linux extensions such as RTLinux, for example). The net effect of both of these factors is greatly to increase development time, and generally also to tie you to a specific hardware/software combination. The major advantage gained by the dualtier, trusted-vs.-untrusted layer solution is the ability to lash together functional, but hard-to-guarantee features on the untrusted layer, using off-the-shelf software and hardware components.

The crucially important technical advantages of our method of putting together our complex embedded system are, therefore:

- The real-time characteristics of any given hard module can be tuned right down to the CPU-cycle level, if desired.

- Changes to any one real-time module don't directly impact the timing properties of any of the other modules.

- Standardizing communication protocols amongst the various modules establishes a "firewall" of sorts, which is useful both for testing purposes (asyet-unbuilt modules can be simulated with a piece of external hardware) and for future upgrades (modules can be replaced with updated versions as long as a consistent software interface is maintained).

- Reuse of hardware modules in other projects is very easy, since it is the *system* that is project-specific, not the individual parts.

- Because access to complex peripherals is abstracted at a fairly high layer (through the operating system running on the untrusted soft-task controller), it's possible to swap out these components for functionally equivalent parts without writing custom device drivers.

In fairness, at this time I should also point out the downsides of the multi-module way of doing things:

The overall bill-of-materials cost for a multi-module system is likely to be much higher in the long term. This is not likely to be a big factor for prototype or short-run construction, where setup costs dominate the unit price. For mass-production, however, the price advantages of a uniprocessor system become progressively more attractive. Note, though, that for low-volume or unique applications, the higher BOM cost of the multiprocessor system may be partially or completely offset by the high cost of obtaining required evaluation hardware for the devices used in the "cheap" uniprocessor design, so the development method I describe here is likely to work out cheaper, per unit, for low-volume designs.

■ Power consumption and physical size will be larger than for a fine-tuned system.

In closing this section, I'd like to rebut one commonly-raised argument against multiprocessor systems: Many people believe that by introducing multiple microcontrollers, you are increasing the number of possible points of failure and thereby making the overall system inherently less reliable. The most succinct counter-argument to this, to which I subscribe, is that conceptually, the same bugs and design shortcomings will exist whether a particular set of features A, B, C are implemented on one processor or three individual processors. Keeping the three functions physically separate prevents them from interfering in each others' address spaces, and also allows fast system recovery—because if, say, processor B crashes, processors A and C can continue to operate unaffected while B reboots.

It is, of course, true that adding more silicon increases the possibility of "SEUs" (single-event upsets) caused by environmental stresses such as incident radiation, simply because there is more silicon real estate to be affected by such factors. This is, however, a relatively subtle point and is unlikely to be an overriding concern in the majority of systems to be built by readers of this book.

### 2.2 Candidate Microcontrollers for 'Hard' Tasks

Given that we need to choose a microcontroller family to handle the real-time parts of our system, let's first create a short list of rules for selecting this family:

- Assemblers and compilers must be freely available, either from the manufacturer or as a result of open-source efforts such as gcc.

- Device programming hardware must either be low-cost or simple enough to build at home using off-the-shelf parts.

- Parts to be used must be available ex stock from major mail-order distributors such as Digi-Key, Newark, and others, with no minimum purchase requirements.

- Device family must contain parts spanning the widest possible variety of ROM, RAM and peripheral requirements, with as much firmware and hardware design commonality as possible.

- Ideally, the parts chosen should enable easy implementation of a slave SPI interface, but this isn't vital (and SPI is extremely simple to bit-bang, anyway).

There are three obvious targets that present themselves immediately: 8051, Microchip PIC®, and Atmel AVR®. The ancient 8051 is indubitably the world's best-known candidate for 8-bit applications, so we'll start by examining this family briefly. It's very inexpensive, available from an unparalleled number of sources (Atmel, Philips, Winbond, Cypress, and Dallas/Maxim are just a few of the vendors with standard 8051 parts; dozens more have 8051-cored ASICs and ASSPs), and the basic architecture is familiar to most embedded engineers. There are numerous high-quality tools and reference designs, and megabytes of sample sourcecode available.

The main reason I have chosen to avoid the 8051 family is because of the lack of standardization across manufacturers. No single manufacturer carries an 8051 variant to suit every single application need, and almost every manufacturer has added somewhat proprietary features to the core or peripherals. Because of the long history of this part, it is even common for a given manufacturer to have two or more completely different lines of 8051-cored parts, with different family trees, idiosyncrasies and programming hardware and software tools. Some 8051 sub-families require external programming hardware; some have in-system programming capabilities, many do not have flash memory, and in order to migrate from one variant to another may require investment in relatively expensive programming hardware. It's possible to avoid some of this nonstandardization by sticking to a set of "vanilla" 8051-cored parts that are implemented nearly identically across manufacturers, but this also means avoiding use of most of the 8051s with interesting nonstandard peripherals; LCD controllers, USB, on-chip A/D and D/A converters, expanded ROM or RAM, in-circuit programming, etc. It also means that, in a modular design where each microcontroller has minimal duties, you will likely be spending far too much on over-specified microcontrollers. For instance, you don't need kilobytes of RAM or ROM for a simple stepper motor controller!

As a secondary, but still relevant point, the 8051's architecture is positively archaic. The upside of this is that compiler vendors understand it very well, and commercial compilers for the 8051 are about as good as they're going to get. The downside is that even the best 8051 compiler (arguably, Keil's product) is unavoidably less efficient than good compilers targeted at more modern processors. Worse still, the only halfway decent open-source C compiler for the 8051 (sdcc) is exactly that—only halfway decent. And writing and maintaining large volumes of 8051 assembly language is irritating. It's an entirely justifiable effort if you're making large volumes of something or have another good reason to pick that architecture, but if you're trying to follow the path of least resistance to build a low-volume system with the minimum possible personnel resources, other microcontrollers are a better investment.

In my opinion, therefore, 8051 variants are a great choice when you have a specific application in mind, and you are looking for a one-chip solution. Because of the anarchic differences between different vendors' sub-families, and the fact that no single vendor carries completely code-compatible parts to suit every application, I feel that 8051 isn't such a good choice for modular applications where you anticipate the need to use many tiny microcontrollers in a single project. The workload required to keep code mobile amongst different 8051 variants with disparate peripherals is quite significant. If, however, you are experienced with the 8051, there is no reason why you can't apply that knowledge to the techniques in this book.

For the projects you will find here, I have chosen to use the Atmel AVR series of microcontrollers. These parts are all flash-based; the family offers a reasonably wide range of functionality, and the instruction set is easy-to-learn and to a large degree common amongst family members. Under most circumstances, AVRs are programmable in-system or in an external socket using a simple-to-manufacture parallel port cable. The official STK500 development board, should you wish to acquire it, is cheap (\$79 is the current list price) and fully-featured. A functional Windows IDE and assembler are free from Atmel, a port of gcc is also available and supported by Atmel, and there are freeware assemblers and other tools for UNIX-based operating systems as well as Windows.

Another ubiquitous microcontroller family, commonly used in low-volume and hobbyist applications, is the Microchip PIC. This family meets essentially all of the requirements in the preceding list. I have not chosen to use it, however, simply because it is slightly harder to learn and use than AVR. (By the way, I base that comment on my own experience in learning the two cores, as well as commentary I have read from neophytes asking for help and advice. This is, however, one of those potentially controversial topics I warned about in the introduction. I'm certainly not condemning the PIC as a hard-to-use maverick, I'm simply pointing out that many people seem to find the AVR family easier to use). One other downside to the PIC family is that the "official" entry-level development kit (PICstart Plus) is more expensive than the STK500—almost three times the price, in fact—and it's nowhere near as flexible, being simply a dumb chip-burner with no prototyping functionality at all.

There are a couple of other reasonably popular microcontroller families that we could have considered, and you may wish to investigate them yourself. The Texas Instruments MSP430 family, for example, is a very interesting range of parts. It combines a 16-bit RISC core (some variants have a bonus hardware multiplier) with various useful peripherals, at an attractive price point. The parts are flash-based and support JTAG debugging using an inexpensive parallel-port or USB-based wiggler; a most useful feature. The downsides to the MSP430 are prototyping issues due to the small packages used, and also interfacing problems arise due to the fact that they are 3.3V parts. However, if you're trying to cut down your power budget, or you're looking for a high-performance core that's inexpensive and well-supported by a major vendor, MSP430 is a good choice.

Another micro that is worth at least a quick look is the range of 8-bit devices from Rabbit Semiconductor, http://rabbitsemiconductor.com/. These parts are derived from the ZiLOG Z-180, so depending on your background you might not have too much of a learning curve. They are firmly targeted at connected applications; Rabbit supplies a free TCP/IP stack and provides several evaluation boards and fairly low-cost, end-application-integratable CPU modules, some of which have Ethernet onboard. They even have a Wi-Fi kit, although it's rather expensive. The main downsides to Rabbit are the small size of the company, which argues against long-term availability (however, they have been around for several years and seem to enjoy good popularity in the hobbyist market), and the fact that their free "Dynamic

C" compiler is horribly nonstandard; it's tedious and most inelegant to port code into or out of a Rabbit design. There is an ANSI C compiler available, but it is buyware. Arguments in favor of Rabbit are low entry cost (all the basic tools are free and the development hardware is reasonably priced), ease of low-volume manufacture (since Rabbit supplies the chips ready-to-run, already soldered down to a board, if you wish), and a rich feature set (large flash memory, large RAM, fairly simple programming with a C-like language as well as assembly language, and a lot of ready-to-use application-specific code, particularly in the realm of TCP/IP networking protocols). Possibly the most compelling argument for Rabbit, however, is the fact that you can migrate from one-time prototype production directly to low-volume manufacturing (a few hundred pieces a year, perhaps) without any need to redesign.

### 2.3 The Atmel AVR and its Development Hardware Up Close

After some careful thought about the pros and cons, I have decided to use a single type of AVR chip for all the example projects in this book but one. The reasons for this are twofold: first, to reduce the number of separate parts you need to acquire in order to build these projects (and to allow you to use the same chip for different projects, if you wish), and second to avoid too much explanatory text devoted to pedestrian compatibility issues. The particular AVR I have chosen is the ATtiny26L, which provides a good cross-section of the peripherals available in the AVR family. Migrating code snippets to other AVRs is not difficult.

The AVR series consists of a fairly broad range of hybrid-bit-width microcontrollers (nominally 16-bit code word, 8-bit data bus and ALU) sharing a common instruction set and differing primarily in the on-chip peripherals and package options. These devices don't show a clear genealogical relationship to any other microcontroller core I'm aware of, but some variants do show superficial signs of having been designed for people migrating away from the 8051 (the 40-pin AVRs are in a very similar pinout to a standard 40-pin 8051, for instance). AVR is a Harvard-architecture RISC core with 32 8-bit general-purpose registers, named R0–R31. These registers are mapped into the core's data address space at address \$00-\$1F. Registers R26–R31 have a secondary function for indirect addressing modes; they are divided into pairs named X (R26–R27), Y (R28–R29) and Z (R30–R31). Any of these three paired registers can be used as a 16-bit pointer into data RAM (the first

register named is, in each case, the less significant byte of the address word). Most instructions can operate on any register; a few instructions (such as word-add, word-subtract, and load immediate) can operate only on a subset of the registers, R16–R31.

The AVR core also has a separate 64-byte I/O address space to interface with the on-chip peripherals. All of these peripheral control registers are conveniently mirrored in the general data address space at locations \$20-\$5F, so that you can access them with different addressing modes if you wish. The ATtiny26L also has 128 bytes of SRAM from \$60-\$DF, and the remainder of the data address space is unimplemented. Unlike PIC variants that have a limited-depth hardware stack separate from the processor's other address spaces, AVR supports a traditional stack in the on-chip SRAM. The stack pointer is simply an 8-bit register in the I/O address space.

Some other features of the tiny26L, in no particular order, are:

- 128 bytes of EEPROM, useful for storing configuration and calibration data, or failure information for postmortem analysis.

- A simple but very flexible "USI" (Universal Serial Interface) peripheral, configurable to act as an I<sup>2</sup>C, SPI or asynchronous serial port. For trademark reasons, the I<sup>2</sup>C mode is referred to in Atmel literature as Two-wire, and the SPI mode is referred to as Three-wire.

- Two timer/counters, configurable in a variety of modes. One of these timers can be programmed to provide two PWM channels with positive and inverted outputs.

- Eight analog-to-digital converter channels.

- Brownout detector, configurable for 3.3 V or 5 V operation, and watchdog timer.

- In-system programming capability using the built-in SPI interface.

One important fact to note about in-system serial programming is that the micro-controller needs to have a core clock source. Simply providing the SPI data clock is not enough! This means that if you're tinkering with the fuse settings, you have to be careful that you don't disable the system clock. The designs in this book all use an external crystal oscillator. It is unlikely, though not entirely impossible, that you'll

get yourself into a "clockless" situation with such circuits. However, in designs that use the AVR's internal RC oscillator and that re-use the clock input lines for other functions, there is a real hazard that you can disable the device by selecting an external clock mode. To recover from this, you can tristate your external hardware (or lift a CPU pin) and feed in an external clock temporarily.

In the same vein, AVR fuse settings allow you to disable the reset input and use the pin as a GPIO. If you do this, you cannot use serial in-system programming; you must use a parallel programmer. The STK500 is a suitable piece of hardware.

These issues are by no means unique to the AVR family; most microcontrollers that support in-system programming have the same sort of limitation. These problems are also not, as a rule, very important for hobbyist circuits, which typically use socketed DIP microcontrollers. Once you start etching PCBs for your designs, however, it becomes very attractive to use surface-mount packages for size and cost reasons; be careful not to paint yourself into a corner when you're upgrading the firmware on an assembled PCB. By the way, note that Atmel ships AVRs from the factory with an internal RC clock source selected by default, so that you can stuff your board with blank, factory-fresh chips and program them later over the SPI interface.

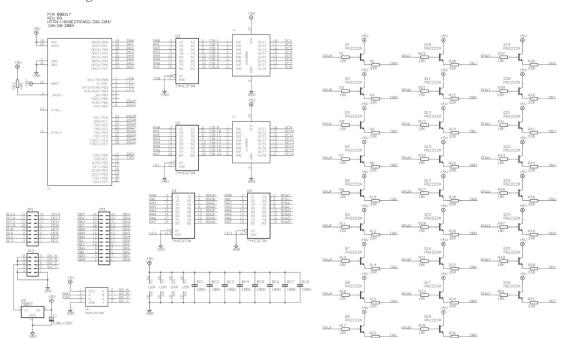

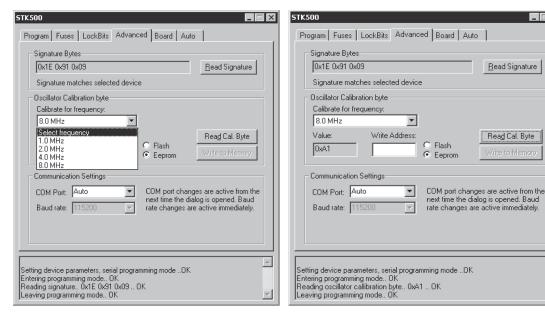

What about firmware development tools? There are a number of products you can use for compiling and burning AVR code. In order to make the example source-code in this book as easily portable between toolchains as possible, I have written it entirely in assembly language. The software development environment I used was Atmel's free AVR Studio for Windows, version 4.08, in conjunction with the STK500 evaluation board. AVR Studio is included on the CD-ROM with this book in the "utils/AVR Studio 4.08" directory, and I strongly advocate using it. However, if you need to use a different assembler (for example, if you're developing under Linux), please try to use the standard Atmel include files, or at least duplicate whatever snippets you need, rather than writing your own set of symbols to describe the registers in the chip. It will be very annoying—to you as well as to other luckless souls updating your work—to have to port code to another member of the AVR family if you use hand-rolled register and bitfield names.

The STK500 is a very flexible, serial-controlled development board that directly supports all of the DIP-packaged AVR chips and, with the STK501 adapter board,

the larger 64-pin surface-mount parts. It can be used to burn microcontrollers inserted in the DIP sockets on the STK500 itself, or it can burn devices already mounted onto your subassemblies, via an in-system-programming cable. It sports eight push-buttons and eight LEDs, and it brings all the I/O lines to 100 mil headers - so you can do some or all of your code debugging directly on the development board. The onboard supervisor microcontroller that manages the STK also allows you to program various clock rates for the device under test, which is a boon to debugging some types of problems—bringing the clock down REALLY slow lets you examine signal state changes in slow motion. For those of you struggling under the evil oppression of a legacy-free PC with only USB ports, the STK500 also works perfectly over a USB-to-serial adapter.

One aspect of the STK500 that is slightly unusual is that you have to set up—by hand—the connections between the device under test and the clock/programming nets required to access it. This is not documented as well as you'd probably like—and it isn't documented at all for some new devices like the ATtiny26L, at least at the time of writing. For the projects in this book, you should take note of the following:

- Your ATtiny26L chip should be inserted in the blue socket labeled SCKT3700A1.

- The ISP6PIN header should be jumped to the SPROG1 (blue) 6-pin header.

- XT1/XT2 on the PORTE/AUX header should be jumped to PB4/PB5 (respectively) on the PORTB header.

- RST on the PORTE/AUX header should be jumped to PB7 on the PORTB header.

- While I was testing the code in this book, I generally had PORTA jumped to the LEDS connector, so that LED0-7 reflect the state of PA0-7, and I jumped SW0-3 on the SWITCHES header to PB0-3 on the PORTB connector.

- Jumpers should be set as follows: VTARGET, AREF, RESET, XTAL1 all shorted, OSCSEL pins 1-2 shorted, BSEL2 open.

All the cables required to perform the above interconnections are shipped as part of the STK500 package.

A final note on AVR Studio: The current version of this program can be rather sensitive to the presence of software that installs filesystem hooks. If you are having difficulty building code (typically, the symptom you will get is that you hit F7 to build, and nothing appears in the output window), try disabling any antivirus software or automatic file versioning utility you have running in the background. This conflict is known to occur, on some systems at least, with both Norton Antivirus and Vet.

#### 2.4 Candidate x86-based SBCs for 'Soft' Tasks

The reason for choosing an Intel-type PC-compatible SBC rather than a proprietary or semi-proprietary architecture based around some RISC microcontroller is primarily ease of development, followed closely by cost. There are numerous readily-available RISC-cored system-on-chip devices (and SBCs based on these parts) which would have adequate processing performance for the E-2 project, and MUCH leaner power requirements. However, the SBCs based on these devices are, by and large, very low-volume, expensive appliances, and developing for and interfacing to them presents significantly greater engineering challenges than simply attaching peripherals to standard PC ports and installing a pre-built driver. By using a hardware platform that is essentially just an off-the-shelf PC-compatible, we can concentrate on the application at hand, rather than spending time on creating a toolchain, configuring and compiling a compatible kernel, and working out the minutiae of interfacing the peripherals we need to use. Our development process is thereby greatly accelerated; refer to the next chapter for a more detailed analysis of this point.

If your requirements are such that you absolutely MUST have low power consumption in the master controller, then you do have a few options. Several companies—including Advantech—sell SBCs based on Intel's XScale® CPU; for example, look at the VIPER product from Arcom, <a href="http://www.arcom.com/">http://www.arcom.com/</a>. These boards are generally built on the standard 3.5" biscuit form factor (see the following) and are supported with ARM-Linux. If you are willing to consider more deeply-embedded solutions running leaner operating systems, there are even more options for you, such as the LPC-xxxx series of evaluation/prototyping boards from Olimex, <a href="http://www.olimex.com/">http://www.olimex.com/</a>. These boards are based around the new Philips LPC2000 series of ARM7-cored microcontrollers; they're supported by GNU tools, simple to program, and the offerings from

Olimex are very reasonably priced (around \$60). Due to RAM limitations, you won't be able to use Linux on these boards; they're best suited to proprietary OS-less environments, or very small operating systems such as uCos-II.

Our selection of x86 leaves us a lot of territory from which to choose, however. There are numerous vendors offering single-board x86-Linux-compatible computers based around processors ranging from the 80386 (in the form of the Intel i386EX embedded controller) all the way up to high-end multiprocessor Pentium 4 and even 64-bit boards<sup>4</sup>. These boards are readily available in a variety of largely standardized form factors:

- 3.5" biscuit. This form factor has the same footprint as a 3.5" disk drive. Power input is via a 4-pin connector carrying +5 V, +12 V and two ground returns, the same type found on a hard disk or CD-ROM drive.

- 5.25" biscuit. This form factor has the same footprint as a 5.25" disk drive. Generally, the power input is via an old AT-style (not ATX!) connector.

- ISA or PCI processor module cards, intended to plug into a passive backplane alongside peripheral cards with the same bus architecture. By the way, a common misconception is that multiple CPU cards of this type can be plugged into a single backplane to build a multiprocessor system; this is never the case for ISA boards, and only occasionally true for PCI cards. Unless the card's documentation *specifically* says that it's designed for use in a multiprocessor environment, you should assume that it can't operate this way. Even if it is possible to build multiprocessor systems around a particular CPU card, a specialized backplane will almost certainly be required. In many cases, these "multiprocessor" backplanes actually have no common connections except the power rails; any inter-processor communications you wish to implement have to be routed through Ethernet or some other user-supplied interconnect mechanism.

- Mini-ITX motherboards. This form factor is mechanically a subset of the standard ITX board used in desktop PCs, and it has a connector for a standard

<sup>&</sup>lt;sup>4</sup> Some vendors still sell systems based around older x86 processors—80186-compatibles are quite common—but we won't discuss these.

ATX power supply. Mini-ITX implementations extant at the time of writing require +3.3 V, +5 V and +12 V rails.

■ Standard-sized PC motherboards with varying levels of on-board peripheral integration.

The Mini-ITX form factor mentioned previously straddles the line between the "consumer off-the-shelf" and "embedded" markets, and deserves a little additional explanation. At the time of writing, the major vendor of Mini-ITX boards is Via Technologies, <a href="http://www.viavpsd.com/">http://www.viavpsd.com/</a>, but other manufacturers are preparing to release similar products. Among these is Transmeta, who have chosen the Mini-ITX form factor for the evaluation boards for their newest x86-compatible processors. Mini-ITX is a physically cut-down (170 × 170mm), backwards-compatible version of the ITX motherboard form factor; it has screw holes and connector zones designed to mate with a standard PC casing and ATX power supply. Via Technologies vigorously markets this form factor to a sector one might characterize as "consumer embedded" applications; i.e., hobbyist projects built around a PC-compatible motherboard. The TV-out feature included on Via's Epia Mini-ITX range has led to a large number of hobbyists using these boards to build dedicated set-top boxes for playing video content downloaded from the Internet. There are also quite a few commercial thin client sorts of applications built around these boards.

Via's latest mini-ITX boards are much more embedded-friendly than the older boards (which were basically just a regular PC motherboard writ small). The latest models have PCMCIA and CompactFlash slots and an even smaller outline than Mini-ITX (Via terms this "Nano-ITX"); they are also substantially cheaper than standard 3.5" and 5.25" SBCs based around the exact same chipsets. Speaking of prices, just as a data point for you, Mini-ITX boards start at just under \$90 retail, single-unit pricing, for a complete board with 533 MHz Via Eden CPU and various integrated peripherals; 3D accelerated AGP Super-VGA, two IDE buses, serial, parallel, Ethernet, four USB ports, etc—just add RAM. Pentium-class SBCs (of comparable performance) in 3.5" or 5.25" form factors start at just above \$350 with a similar set of peripherals. However, that isn't the whole story. One major downside to Mini-ITX is that it assumes the availability of an ATX-style power supply. Via's boards, for instance, absolutely require +3.3 V, +5 V and +12 V rails—they won't operate without all of these voltages present. Most SBCs are happy with a single +5 V

rail<sup>5</sup>; they have onboard regulation to provide whatever other core and I/O voltages they require. You should take the cost of a suitable power supply into account when building your system—and also consider issues like size, airflow/airspace requirements, and noise from cooling fans. Remember that most active cooling systems work constantly to pull any dangerous aerosols or dust in the atmosphere right through your system! My suggestion, if you plan to build Mini-ITX into your system (assuming you don't want to design your own power supply from scratch) is to look at the power supply modules manufactured for 1U rack-mount cases. These are standardized in size (hence, interchangeable) and most of them have variable-speed fans, which run only when the power supply is actually in need of active cooling. They also have enough power capacity to supply any peripheral you are likely to add to such a system.

One final comment on Mini-ITX and Nano-ITX—The star of this form factor is most definitely rising. Several manufacturers produce a range of standardized housings, power supplies and slim peripherals designed specifically for Mini-ITX boards. Some of these are intended for "thin client" diskless applications, others for semi-industrial rack-mount installations, and some of them even for set-top-box use. If you want to use the minimum possible quota of custom parts in your design, Mini-ITX is a great path to investigate.

A very important factor which you should always keep in mind is that consumer-grade PC products are constantly changing. It's extremely difficult to standardize a product if you're building it out of ill-specified parts, and that translates into ongoing costs for you in revising housing designs, re-testing your external circuit and firmware with different motherboard chipsets, and so on. Obviously, this isn't much of an issue for a one-off project, but it is a major sourcing issue for low-volume, long-term ongoing production, where your order quantities aren't high enough to guarantee supply of older parts. As a rule of thumb, if you anticipate the production life of your device

Most (if not all) SBCs have inputs for at least +5 V and +12 V; many have inputs for negative rails too. However, in most cases you'll find that these extra voltages are only passed through to expansion ports; they're not actually used on the SBC. The PCM-5820, for instance, relies only on the +5 V rail. If available, it can use the +12 V rail to achieve a wider swing on the audio outputs, but if you don't want to provide a dual-voltage power supply, just set the audio jumper for "no 12 V" and the board is quite happy to run off +5 V only.

to span six months or more, and it has to be squeezed into a special form factor of any sort, then I strongly advise you to design around an SBC rather than an off-the-shelf motherboard. You'll pay something of a premium, but it will save a lot of time and money in the medium to long term because you won't need to revise cable harnesses, housing designs, power supply requirements, and so on. Remember also that in most jurisdictions, you have to pay for EMI compliance testing every time you make a design change like this, or risk enormous fines!

If you're willing to shoulder the annoyance of (at least potentially) keeping track of several software versions, and your application is not tightly space-constrained, then standard PC motherboard form factors do have a certain appeal—the ATX standard (and by extension, Mini-ITX) specifies a single standardized square cutout connector zone. Every motherboard ships with a small springy steel plate that mates with this connector zone and provides precise cutouts to match whatever connectors are provided on that specific motherboard. This neatly takes care of the EMI problems I mentioned earlier—the biggest annoyance (besides the fact that ATX motherboards are relatively large, and the volume of airspace you need to keep clear to match the ATX clearances standard fully is pretty vast) is that as supplies of a particular motherboard dry up, you'll need to test and qualify your software distribution on new platforms. If your application is the sort of animal that requires ongoing software updates, you have to decide whether to make a super-intelligent software upgrade bundle that can work out what kind of hardware it's running on and configure itself appropriately, or keep track of which users have which hardware versions. The latter approach is easy while you have only a few customers, but once your userbase swells, it becomes a big exercise in database management, particularly once a few units have been in for repair and have had parts "upgraded"—because you can no longer use simple serial number range checks to know what's inside a particular unit. Your situation may have special circumstances, but when I've been involved in a project like this, it has always been less work, ultimately, to build a single software bundle that works on all supported hardware versions. At the very least, design your system in such a way that it's possible for the software to determine what kind of hardware it's running on before it needs to do any hardware-specific startup tasks. That might sound crazy, but unless you design with this idea in mind, it's not uncommon to run into chicken-and-egg situations where the only way you can identify

some piece of hardware is by assuming the existence of some other piece of hardware, probing which may crash the system if it doesn't contain this particular device.

On the topic of housing your system, if you're building a device in any reasonable production quantity, you will want a professional-looking enclosure for it. Jiffy boxes work, but they're ugly. Unfortunately, the tooling cost for a custom plastic enclosure is prohibitive—tens of thousands of dollars at minimum. A much cheaper option, which people rarely seem to consider, is bent sheet-steel. Numerous metal enclosure shops can build you quite complex shapes at a surprisingly low cost. Modern metalworking shops use CNC laser cutting tools on the raw sheet stock to make holes and tabs of practically any shape. The parts are then bent by hand, and spotwelded where necessary. Fasteners—threaded posts ready to accept a nut, tapped posts to accept a screw, reinforced spots for rivets, and so on—are permanently bonded to the sheet parts using a press apparatus. The parts can then be painted and baked, if desired. As a data point for you, a production run of around one hundred pieces, with an exterior paint job and approximately the same complexity as a desktop PC's casing, manufactured locally in the United States, will cost around US\$60 per piece. It's entirely possible to get even cheaper prices if you shop around—there are literally thousands of metal shops that can do this sort of work.

Another possible housing solution is to use a section of aluminum extrusion with custom-punched end plates. This type of housing works very well with 3.5" SBCs and other boards that run all their important connectors to an edge. It's less workable when you need to mount lots of connectors on the end panels using flying leads. (Cheap external modems were often manufactured using this method a few years ago). If you're contemplating this option, you may want to visit <a href="http://www.frontpanelexpress.com/">http://www.frontpanelexpress.com/</a>, where you can download software to create your custom end-panels and get an instant online quote on production.

In any case, before you sign off on your custom enclosure solution, compare your design with standard products and decide if the customization you've added is really worth it. Remember—if you're using a Mini-ITX board, there are numerous low-profile housings available to you off the shelf in a variety of shapes. You can also think about using a standard 1U 19" ATX rack-mount casing, which will already have a standard connector zone cutout in the back and a suitable, UL-listed power supply—plus, it has the advantage of integrating neatly with a lot of other industrial

equipment. Another subtle advantage of this approach is that if you build a computer system out of FCC-approved parts, you don't need to seek a separate approval for the assembled system—it just rides the approval of its individual components.

## 2.5 The Advantech PCM-5820 Single-Board Computer Up Close

For this text, I have chosen to use the Advantech PCM-5820 single-board computer as my reference platform. This board has a combination of factors working in its favor, which is why I have been working with it for a couple of years:

- It is readily available ex-stock at a reasonable price (around US\$235 at the time of writing; cheaper than many industrial SBCs of much lower performance).

- It is physically quite small, at  $145 \times 102$  mm (it is a 3.5" biscuit) and it is easy to mount.

- Its power requirements are relatively modest for a Pentium-class x86 system; Advantech quotes typical current requirements of 1.5A from a single +5 V rail, although peak current requirements can be as much as 4A. A side benefit of this is that it does not absolutely require active cooling (Advantech ships it with a thin passive heatsink); as long as you don't actually wrap it in a blanket, overheating is unlikely to be a problem.

- The board sports a healthy selection of peripherals and I/O features, making it very easy to interface with a wide variety of external systems.

- The price-performance balance is *very* attractive. The next step down would be a board based on a low-speed Pentium, i486 or even i386 CPU; these boards are just a few dollars cheaper than the PCM-5820, and much less capable. In particular, the integrated USB is a real boon; it allows you to hook in cheap consumer peripherals rather than fiercely expensive PC/104 expansion cards.

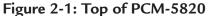

Let's take a moment to examine the PCM-5820 hardware in detail. Figures 2-1 and 2-3 detail photographs of the top and bottom of the board, showing the high level of integration. Note the low-profile heatsink and absence of active cooling. I didn't remove anything from the board to take these photos; this is how the board ships, and it doesn't need any further cooling in most situations.

Figure 2-2: Bottom of PCM-5820

The major hardware features are as follows:

Microprocessor – National Semiconductor Geode<sup>6</sup>. The fastest flavor of this processor available on the 5820 is 300 MHz; some other vendors offer 333 MHz products. Geode is a "Pentium-ish" CPU; it is hard to establish an exact equivalent with an Intel CPU, but the performance is something like an accelerated Pentium 1. It supports the MMX-1 instruction set extensions, but it lacks some Pentium core components such as MTRRs (Memory Type Range Registers). Geode has an architectural equivalent, ARRs (Address Range Registers). It also has an extensive system of software traps that allow it to emulate many standard PC hardware features in firmware; more on this topic later. Very roughly speaking, a 300 MHz Geode is comparable in performance to a 200 MHz Pentium with MMX. Archaeologically, Geode is descended directly from the Cyrix MediaGX processor. It appears to share some history with the early IBM/Cyrix 486SLC (clock-multiplied 486-compatible in an i386SX pinout) and "Blue Lightning" (clock-multiplied 486-compatible in an i386DX pinout) processors. Because of the slightly unusual architecture, there are some behavioral oddities in the Geode platform; we'll discuss most of these in the text to follow.

The Geode range of x86-compatible Internet appliance processors was sold by National Semiconductor to AMD, in a deal announced in mid-2003. However, as at the time of writing, I have yet to see an AMD-branded Geode chip.

- RAM There is a single standard SODIMM slot supporting memory sizes up to 256 MB. The board uses 3.3V unbuffered PC100 SDRAM. In our examples, we will be assuming a system with 64 MB RAM.

- Ethernet The board has a Realtek RTL8139 10/100 Ethernet MAC; well-supported and relatively trouble-free. There is a network boot extension available in the system BIOS, should you care to use it.

- USB The system has two USB 1.0 OHCI-compatible ports provided by the CS5530 companion IC. I have read scattered reports of problems (lockups and incompatibilities) with the USB implementation in this chip, mostly with high-bandwidth devices (video capture pods, storage devices and LAN adapters). To date, I have not encountered any problems of this nature, and it may be that these issues only affect older operating system kernels.

- Serial There are two serial ports, one of which is RS-232-only, and the other of which can be configured as either RS-232, RS-422 or RS-485.

- Parallel The board features a standard parallel port, configurable for SPP, EPP or ECP modes. This port is very useful as general-purpose I/O.

- Audio The CS5530 companion IC on-board has an AC97 codec interface. At the time of writing, current production of the PCM-5820 is shipping with a Realtek ALC201 codec. Older production used an Analog Devices codec. By and large, this hardware difference should not require any software modifications. The board has line-level and microphone-level inputs, line-level output, and individual speaker drive outputs. It is not capable of delivering much power to the speaker outputs, so for anything other than headphone connections you will probably want an external audio power amplifier.

- Video The 5820 has a standard analog VGA output, as well as a header for connecting to parallel TFT LCDs. An LVDS transmitter IC (and associated LVDS output connector) is optionally available on some board variants. Supported resolutions range up to 1280 × 1024 (at 8 bpp, on CRT only) or 1024 × 768 (at 16 bpp, on CRT or LCD). Passive panels are not supported; the CS5530 requires additional external DRAM to support passive displays, and Advantech has not allocated space on the board for this additional RAM.

- Mass-storage There is a standard floppy drive header supporting two drives. More usefully, there is a single standard IDE bus (with a 44-pin 2 mm pitch "laptop" type connector) and a bootable CompactFlash slot on the secondary IDE port. Note that the CompactFlash slot is wired in True-IDE mode, and it is therefore not possible to use nonstorage devices or to "hot swap" CompactFlash cards. (The CompactFlash specification requires a power-cycle in order to swap media if the socket is run in True-IDE mode. This requirement has to do with the length of the pins in the socket, which control power sequencing; hot-swap will sometimes work on a True-IDE slot, especially if you push the card in swiftly and firmly, but it can't be guaranteed, and you should avoid trying it because there is a risk of damaging the card).

- Expansion bus Although the Geode system uses a PCI architecture, the 5820 does not offer a means to connect PCI peripherals. The board has a standard PC/104 header, essentially an ISA interface.

- Miscellaneous A single PS/2 port allows connection of a keyboard and mouse by way of a Y-cable, supplied with the board. There is also a port to connect an IrDA transceiver or CIR receiver module; the inbuilt IR UART can be configured for various infra-red decoding modes including ASK, FSK and IrDA. (Enabling infra-red functionality usually disables normal use of the second serial port).

If, for whatever reason, you need to seek an alternative supplier of boards, and you're trying to find something similar to the hardware described in this book, there are many options for second-sourcing. (This is yet another advantage of choosing a PC-based architecture). Here is a short list of compatible, or at least broadly similar products from different vendors, with comments on their differences from the PCM-5820. You should be able to run the example code in this book on any of these boards with few or no modifications:

| Vendor                                      | Model          | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

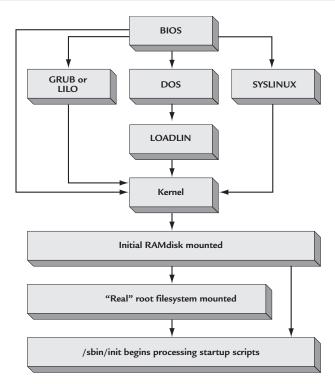

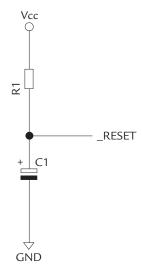

|---------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|